# RACAL INSTRUMENTS 3352 VXI Rubidium

PUBLICATION NO. 980900

EADS North America Defense Test and Services, Inc. 4 Goodyear, Irvine, CA 92618 Tel: (800) 722-2528, (949) 859-8999; Fax: (949) 859-7139

> info@eads-nadefense.com sales@eads-nadefense.com helpdesk@eads-nadefense.com http://www.eads-nadefense.com

#### PUBLICATION DATE: April 18, 2007

Copyright 2004 by EADS North America Defense Test and Services, Inc. Printed in the United States of America. All rights reserved. This book or parts thereof may not be reproduced in any form without written permission of the publisher.

# THANK YOU FOR PURCHASING THIS EADS NORTH AMERICA DEFENSE TEST AND SERVICES PRODUCT

For this product, or any other EADS North America Defense Test and Services, Inc. product that incorporates software drivers, you may access our web site to verify and/or download the latest driver versions. The web address for driver downloads is:

http://www.eads-nadefense.com/downloads

If you have any questions about software driver downloads or our privacy policy, please contact us at:

info@eads-nadefense.com

# WARRANTY STATEMENT

All EADS North America Defense Test and Services, Inc. products are designed and manufactured to exacting standards and in full conformance to EADS ISO 9001:2000 processes.

For the specific terms of your standard warranty, or optional extended warranty or service agreement, contact your EADS North America Defense Test and Services, Inc. customer service advisor. Please have the following information available to facilitate service.

- 1. Product serial number

- 2. Product model number

- 3. Your company and contact information

You may contact your customer service advisor by:

| E-Mail:    | Helpdesk@eads-nadefense.com |       |

|------------|-----------------------------|-------|

| Telephone: | +1 800 722 3262             | (USA) |

| Fax:       | +1 949 859 7309             | (USA) |

# **RETURN of PRODUCT**

Authorization is required from EADS North America Defense Test and Services, Inc. before you send us your product for service or calibration. Call or contact the Customer Support Department at 1-800-722-3262 or 1-949-859-8999 or via fax at 1-949-859-7139. We can be reached at: <u>helpdesk@eads-nadefense.com</u>.

### **PROPRIETARY NOTICE**

This document and the technical data herein disclosed, are proprietary to EADS North America Defense Test and Services, Inc., and shall not, without express written permission of EADS North America Defense Test and Services, Inc., be used, in whole or in part to solicit quotations from a competitive source or used for manufacture by anyone other than EADS North America Defense Test and Services, Inc. The information herein has been developed at private expense, and may only be used for operation and maintenance reference purposes or for purposes of engineering evaluation and incorporation into technical specifications and other documents which specify procurement of products from EADS North America Defense Test and Services, Inc.

# DISCLAIMER

Buyer acknowledges and agrees that it is responsible for the operation of the goods purchased and should ensure that they are used properly and in accordance with this handbook and any other instructions provided by Seller. EADS North America Defense Test and Services, Inc. products are not specifically designed, manufactured or intended to be used as parts, assemblies or components in planning, construction, maintenance or operation of a nuclear facility, or in life support or safety critical applications in which the failure of the EADS North America Defense Test and Services, Inc. product could create a situation where personal injury or death could occur. Should Buyer purchase EADS North America Defense Test and Services, Inc., its officers, employees, subsidiaries, affiliates and distributors harmless against all claims arising out of a claim for personal injury or death associated with such unintended use.

# FOR YOUR SAFETY

Before undertaking any troubleshooting, maintenance or exploratory procedure, read carefully the **WARNINGS** and **CAUTION** notices.

CAUTION RISK OF ELECTRICAL SHOCK DO NOT OPEN This equipment contains voltage hazardous to human life and safety, and is capable of inflicting personal injury.

If this instrument is to be powered from the AC line (mains) through an autotransformer, ensure the common connector is connected to the neutral (earth pole) of the power supply.

Before operating the unit, ensure the conductor (green wire) is connected to the ground (earth) conductor of the power outlet. Do not use a two-conductor extension cord or a three-prong/two-prong adapter. This will defeat the protective feature of the third conductor in the power cord.

Maintenance and calibration procedures sometimes call for operation of the unit with power applied and protective covers removed. Read the procedures and heed warnings to avoid "live" circuit points.

Before operating this instrument:

- 1. Ensure the proper fuse is in place for the power source to operate.

- 2. Ensure all other devices connected to or in proximity to this instrument are properly grounded or connected to the protective third-wire earth ground.

If the instrument:

- fails to operate satisfactorily

- shows visible damage

- has been stored under unfavorable conditions

- has sustained stress

Do not operate until, performance is checked by qualified personnel.

# **Racal Instruments**

# **CE** Declaration of Conformity

| We |                                                                                                                                                                           |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | Racal Instruments Inc.<br>4 Goodyear Street<br>Irvine, CA 92618                                                                                                           |

|    | declare under sole responsibility that the                                                                                                                                |

|    | 3352-GPS VXI RUBIDIUM , P/N 407919, -001, -002 conforms to the following Product Specifications:                                                                          |

|    | EMC: EN61326:1998 +A1: 1998 +A2: 2001                                                                                                                                     |

|    | FCC CFR 47, PART 18 SUBPART B CLASS A                                                                                                                                     |

|    | ICES-003 ISSUE 4: February 2004 CLASS A                                                                                                                                   |

|    | Supplementary Information:                                                                                                                                                |

|    | The above specifications are met when the product is installed in a Racal Instruments certified mainframe with faceplates installed over all unused slots, as applicable. |

|    | The product herewith complies with the requirements of the Low Voltage Directive 73/23/EEC and the EMC Directive 89/336/EEC (modified by 93/68/EEC).                      |

|    | Irvine, CA, April 13, 2005<br>VP of Engineering<br>Karen Evensen                                                                                                          |

|    |                                                                                                                                                                           |

This page was left intentionally blank.

# **Table of Contents**

| Chapter 1                |

|--------------------------|

| INTRODUCTION             |

| General Description1-7   |

| Product Configuration1-7 |

| VX405C1-7                |

| M2121-1                  |

| M2131-1                  |

| M17081-1                 |

| M2101-1                  |

| M17141-1                 |

| MTBF1-2                  |

| Programming1-2           |

|                          |

|                          |

| Chapter 2                   | 2-1 |

|-----------------------------|-----|

| VX405                       | 2-1 |

| General Description         | 2-1 |

| Purpose of Equipment        | 2-1 |

| Specifications of Equipment | 2-1 |

| Key Features                | 2-1 |

| Electrical                  | 2-2 |

| Mechanical                  | 2-2 |

| Environmental               | 2-2 |

| Bus Compliance              | 2-3 |

| Applicable Documents                  | 2-3  |

|---------------------------------------|------|

| Installation                          | 2-3  |

| Unpacking and Inspection              | 2-3  |

| Handling Precautions                  | 2-4  |

| Installation of M\MA Modules          | 2-4  |

| Installation of VX405C Carrier (3352) | 2-5  |

| Preparation for Reshipment            | 2-5  |

| Functional Description                | 2-5  |

| General                               | 2-5  |

| Interfaces                            | 2-7  |

| I/O and Memory Addressing             | 2-7  |

| Triggers                              | 2-8  |

| Interrupts                            | 2-8  |

| Hardware Configuration                | 2-8  |

| Logical Address                       | 2-8  |

| Modulo Select                         | 2-8  |

| Address Space                         | 2-8  |

| M/MA Module Enable                    | 2-8  |

| Indicators                            | 2-10 |

| Connectors                            | 2-10 |

| Front Panel Connector                 | 2-10 |

| Rear Connectors                       | 2-10 |

| Configuration Registers               | 2-11 |

| VXI Configuration Registers           | 2-11 |

| VXI Identification (ID) Register      | 2-11 |

| VXI Device Type Register              | 2-11 |

| VXI Status/Control Register           | 2-12 |

| VXI Offset Register           | 2-12 |

|-------------------------------|------|

| Special Function Register     | 2-14 |

| Interrupt Control Registers   | 2-14 |

| Trigger Control Register      | 2-14 |

| Operating Instructions        | 2-16 |

| General                       | 2-16 |

| Hardware Configuration        | 2-16 |

| Logical Address Selection     | 2-16 |

| Address Space Selection       | 2-19 |

| M/MA Module Enable            | 2-19 |

| Software Configuration        | 2-19 |

| Required Memory Setting       | 2-19 |

| Triggers                      | 2-20 |

| Interrupts                    | 2-21 |

| M/MA Module Identification    | 2-21 |

| Built in Test and Diagnostics | 2-22 |

| Trouble Analysis Guide        | 2-22 |

| Chapter 3                     | 3-1 |

|-------------------------------|-----|

| M213                          | 3-1 |

| General Description           | 3-1 |

| Purpose of Equipment          | 3-1 |

| Specifications of Equipment   | 3-1 |

| Module Key Features           | 3-1 |

| Oncore M12+ Specific Features | 3-1 |

| Specifications                | 3-2 |

| Mechanical                    | 3-4 |

| Bus Compliance                             | 3-4  |

|--------------------------------------------|------|

| Applicable Documents                       |      |

| Functional Description                     | 3-5  |

| Overview                                   |      |

| M-Module Interface                         | 3-5  |

| Control Logic                              | 3-5  |

| Microcontroller/ UART                      | 3-5  |

| Oncore M12+ Timing Receiver                | 3-6  |

| Power Conversion and Distribution          | 3-6  |

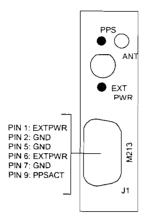

| Physical Layout                            | 3-6  |

| Input/Output Signals                       | 3-7  |

| PPS                                        |      |

| ANT                                        | 3-7  |

| EXTPWR                                     | 3-7  |

| PPSACT                                     | 3-7  |

| GND                                        | 3-7  |

| Identification and Configuration Registers | 3-8  |

| I/O Registers                              | 3-8  |

| M-Module Identification PROM               | 3-9  |

| Operation                                  |      |

| Rubidium Oscillator Communication          | 3-10 |

| Interrupts                                 |      |

| ID Prom                                    | 3-10 |

| Chapter 4                    | 4-1  |

|------------------------------|------|

| M212                         | 4-1  |

| General Description          | 4-1  |

| Purpose of Equipment         | 4-2  |

| Specifications of Equipment  | 4-2  |

| Key Features                 | 4-2  |

| Specifications               | 4-3  |

| Mechanical                   | 4-5  |

| Bus Compliance               | 4-5  |

| Applicable Documents         | 4-5  |

| Installation                 | 4-5  |

| Unpacking and Inspection     | 4-5  |

| Handling Precautions         | 4-6  |

| Installation of M/MA Modules | 4-6  |

| Preparation for Reshipment   | 4-6  |

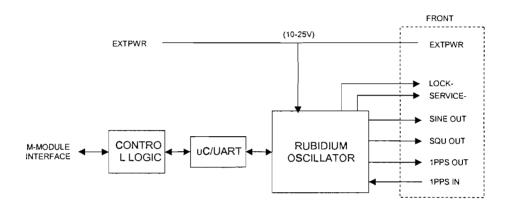

| Functional Description       | 4-7  |

| Overview                     | 4-7  |

| M-Module Interface           | 4-7  |

| Control Logic                | 4-7  |

| Microcontroller/ UART        | 4-7  |

| Rubidium Oscillator          | 4-8  |

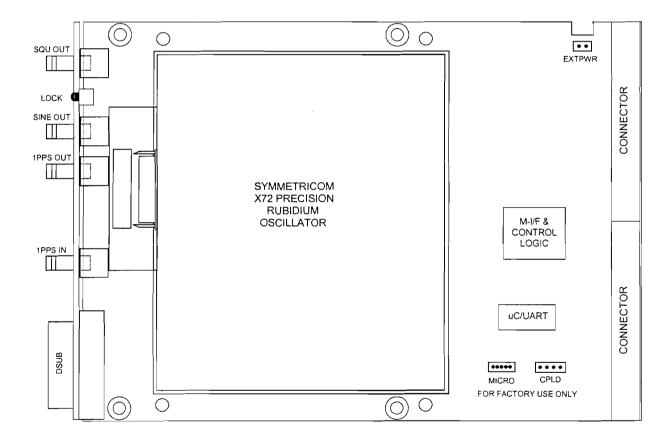

| Physical Layout              | 4-8  |

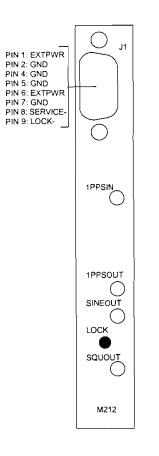

| Input/Output Signals         | 4-10 |

| EXTPWR                       |      |

| LOCK                         |      |

| SERVICE                      | 4-10 |

| 1 PPSIN 4-10                                    |

|-------------------------------------------------|

| 1PPSOUT                                         |

| SINEOUT                                         |

| SQUOUT                                          |

| Identification and Configuration Registers 4-11 |

| I/O Registers 4-11                              |

| M-Module Identification PROM 4-13               |

| Operation                                       |

| Programming                                     |

| Writing Registers 4-14                          |

| Rubidium Oscillator Communication 4-14          |

| Data Format 4-14                                |

| Run Mode Data Format (Customer Mode) 4-14       |

| X72 1PPS Functions 4-18                         |

| X72 1PPS Algorithm Operation 4-19               |

| Changing the "y" Coefficients 4-19              |

| The "y" Coefficients – Factory Default 4-20     |

| The "j" Command 4-20                            |

| The "g" Command                                 |

| Calibration                                     |

| Floating Point Number Representation 4-22       |

| Interrupts 4-25                                 |

| ID PPROM                                        |

| Chapter 5                  | 5-1 |

|----------------------------|-----|

| M1708                      | 5-1 |

| General Description        | 5-1 |

| Interfacing to the M1708   | 5-2 |

| Accessing the Module       | 5-2 |

| EEPROM Identification      | 5-3 |

| Address Decoding           | 5-4 |

| Connectors                 | 5-4 |

| Specifications             | 5-4 |

| Electrical Specifications  | 5-5 |

| Environment Specifications | 5-6 |

| Physical Specifications    | 5-6 |

| Chapter 6                      |

|--------------------------------|

| M2106-1                        |

| General Description            |

| Purpose of Equipment6-1        |

| Specifications of Equipment6-1 |

| Key Features6-1                |

| Specifications                 |

| Mechanical6-4                  |

| Bus compliance                 |

| Applicable Documents           |

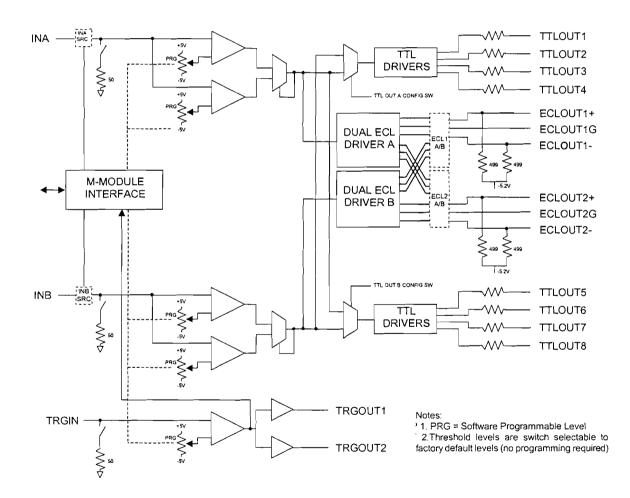

| Functional Description6-5      |

| Overview6-5                    |

| M-Module Interface                         | 6-6 |

|--------------------------------------------|-----|

| Input Comparators                          | 6-6 |

| TTL Drivers                                | 6-6 |

| ECL Drivers                                | 6-6 |

| Trigger Input Comparator and Distribution  | 3-7 |

| Hardware Configuration6                    | 3-7 |

| INA IMP Switch                             | 3-8 |

| INB IMP Switch                             | 3-8 |

| TRG IMP Switch                             | 3-8 |

| INA SRC Switch                             | 3-8 |

| INB SRC Switch                             | 3-8 |

| INA LEVEL Switch                           | 5-8 |

| INB LEVEL Switch                           | 3-8 |

| TRG LEVEL Switch6                          | 5-8 |

| ECL1 Switch6                               | 3-8 |

| ECL2 Switch6                               | 3-8 |

| OUT CFG Switch                             | 5-8 |

| INPUT/OUTPUT Signals6                      | 3-9 |

| ECLOUT1 + and ECLOUT1+6                    | 3-9 |

| ECLOUT2 - and ECLOUT26                     | 3-9 |

| ECLOUT1G and ECLOUT2G6                     | 3-9 |

| TRG6                                       | 3-9 |

| INB                                        | ·10 |

| INA6-                                      | ·10 |

| TTLOUT1-8                                  | ·10 |

| TRGOUT1 and TRGOUT26-                      | 10  |

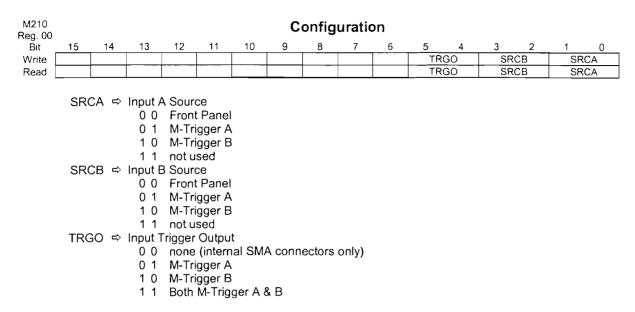

| Identification and Configuration Registers | 11  |

| I/C  | ) Registers                  | 6-11 |

|------|------------------------------|------|

| Mc   | odule Identification         | 6-13 |

| Oper | ration                       | 6-15 |

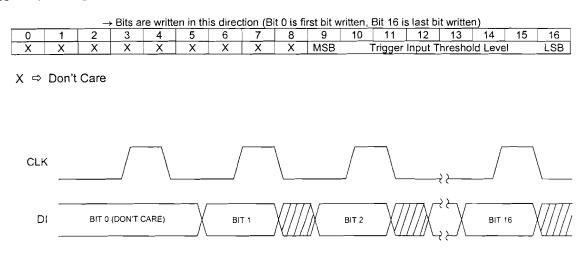

| ĺ    | Programming Threshold Levels | 6-15 |

| I    | ID PROM                      | 6-16 |

| Chapter 7                      |

|--------------------------------|

| M17147-1                       |

| GENERAL DESCRIPTION7-1         |

| Specifications of Equipment7-1 |

| Key Features7-1                |

| Specifications7-1              |

| Mechanical7-2                  |

| Bus Compliance7-2              |

| Applicable Documents7-3        |

| Ordering Information7-3        |

| Functional Description7-3      |

| Overview7-3                    |

| M-Module Interface7-4          |

| Control Logic7-4               |

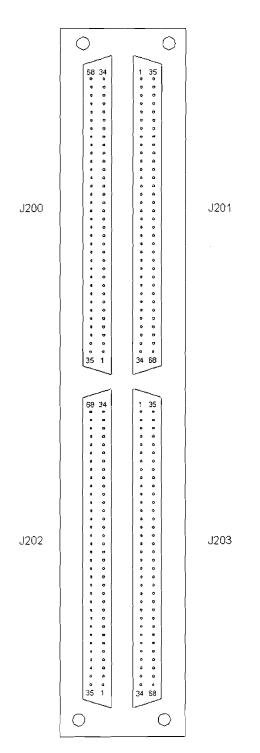

| Front Panel Connectors7-5      |

| J2007-6                        |

| J2017-7                        |

| J202                           |

| J203                           |

| Mating Connectors              |

| Operating Mode                 |

| Register Definitions                                |

|-----------------------------------------------------|

| M1714 ID Register (00h)                             |

| Revision ID Register (02h)                          |

| BIST Command Register (04h) 7-1.                    |

| Status Register (04h)                               |

| Direction Control for Octets 1-8 (0Ah)              |

| Direction Control for Octets 9-16 (0Ch)7-14         |

| Master Write Strobe for Stimulus Data (0Eh)         |

| Master Read Strobe for Response Data (0Eh)          |

| Octet Stimulus / Response Data Register (10h – 2Eh) |

| Chapter 8       | 8-1 |

|-----------------|-----|

| Product Support | 8-1 |

| Product Support | 8-1 |

| Warranty        | 8-1 |

| APPENDIX A: VX405 (P1 & P2) CONNECTORS | . A-1 |

|----------------------------------------|-------|

| APPENDIX B: M213 CONNECTORS            | . B-1 |

| APPENDIX C: M212 CONNECTORS            | .C-1  |

| APPENDIX D: M1708 CONNECTORS           | . D-1 |

| APPENDIX E: M210 CONNECTORS            | . E-1 |

# List of Figures

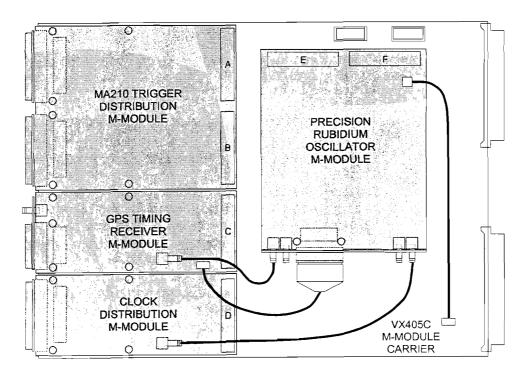

| Figure 2-1, 3352 M/MA Configuration Diagram        | 2-4  |

|----------------------------------------------------|------|

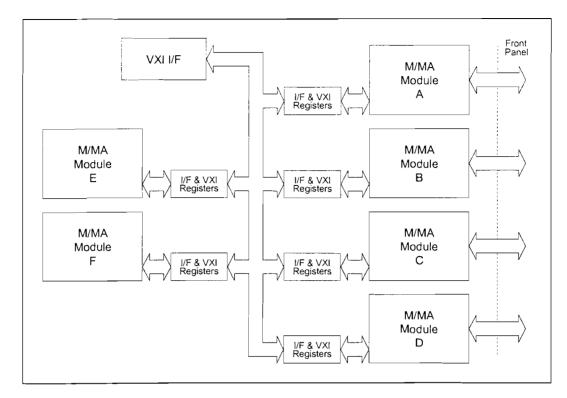

| Figure 2-2, VX405C Functional Block Diagram        | 2-6  |

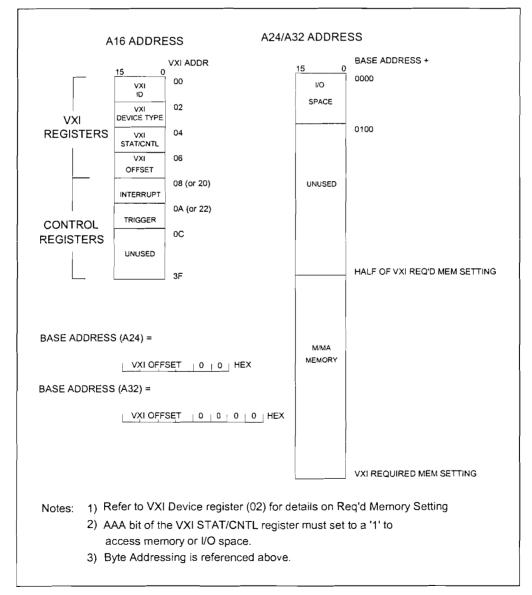

| Figure 2-3, Memory Organization                    | 2-7  |

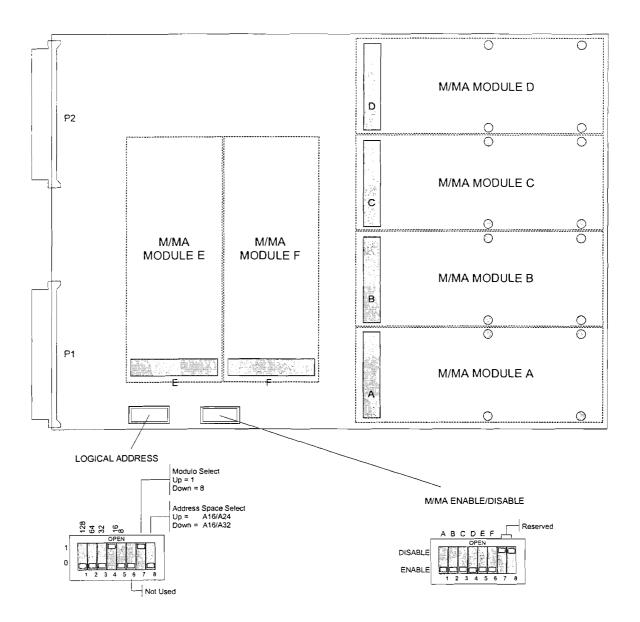

| Figure 2-4, VX405C Hardware Configurable Controls  | 2-9  |

| Figure 2-5, 3352 Front Panel                       |      |

| Figure 2-6, VXI Configuration Registers            |      |

| Figure 2-7, Special Function Registers             |      |

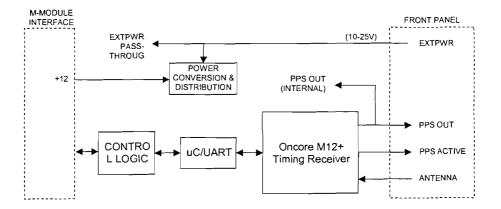

| Figure 3-1, Functional Block Diagram               | 3-5  |

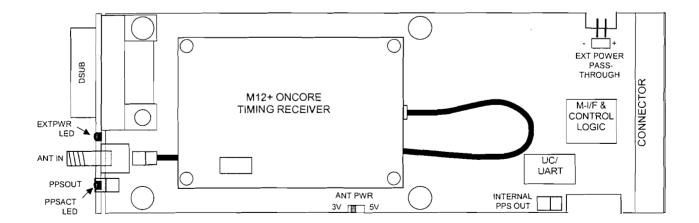

| Figure 3-2, M213 Physical Layout                   | 3-6  |

| Figure 3-3, M213 Front Panel                       | 3-7  |

| Figure 3-4, M213 I/O Registers                     | 3-8  |

| Figure 3-5, ID PROM Access Routine                 |      |

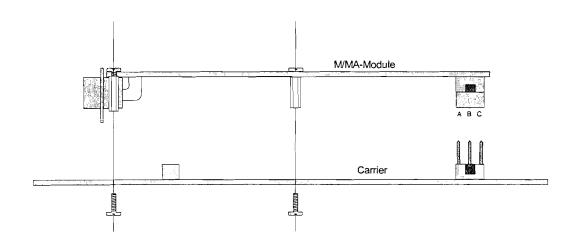

| Figure 4-1, M-MODULE Installation                  | 4-6  |

| Figure 4-2, M212 Functional Block Diagram          | 4-7  |

| Figure 4-3, M212 Physical Layout                   | 4-8  |

| Figure 4-4, M/MA Interface Connector Configuration | 4-9  |

| Figure 4-5, M212 Front Panel                       |      |

| Figure 4-6, M212 I/O Registers                     |      |

| Figure 4-7, ID PROM Access Routine                 | 4-26 |

| Figure 5-1, M1708 Front panel                      | 5-1  |

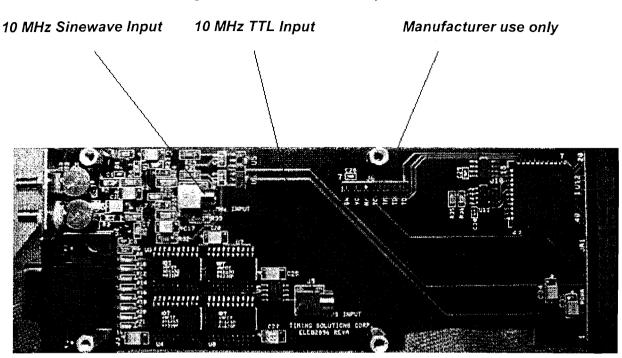

| Figure 5-2, M1708 PWA component side               | 5-2  |

| Figure 6-1, Functional Block Diagram                                                                                                                                                                                                                                           | 6-5                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

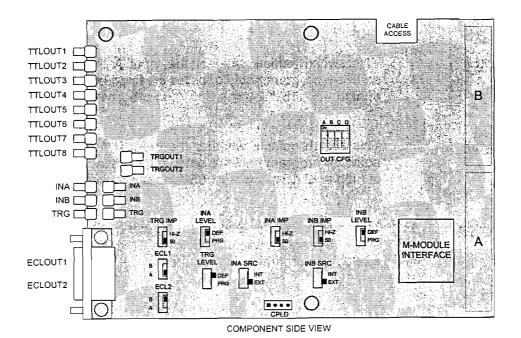

| Figure 6-2, M210 Hardware Configuration Switches                                                                                                                                                                                                                               | 6-7                                    |

| Figure 6-3, M210 Front Panel                                                                                                                                                                                                                                                   |                                        |

| Figure 6-4, M210 I/O Registers                                                                                                                                                                                                                                                 |                                        |

| Figure 6-5, Potentiometer Serial Programming                                                                                                                                                                                                                                   | 6-15                                   |

| Figure 6-6, ID PROM Access Routine                                                                                                                                                                                                                                             | 6-17                                   |

|                                                                                                                                                                                                                                                                                |                                        |

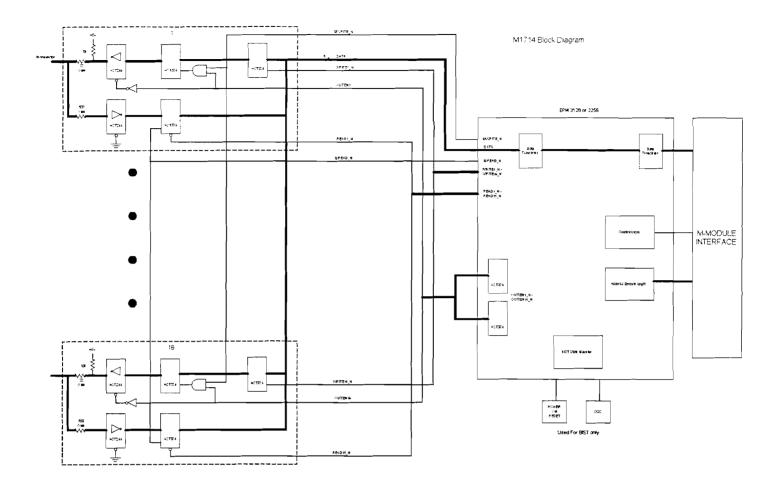

| Figure 7-1, M1714 Block Diagram                                                                                                                                                                                                                                                | 7-4                                    |

| Figure 7-2, M1714 Front Panel Connectors                                                                                                                                                                                                                                       | 7-5                                    |

| Figure 7-3, Command Register Bit Assignment for the M1714                                                                                                                                                                                                                      |                                        |

| Figure 7-4, BIST Status Register Bit Assignment for the M1714                                                                                                                                                                                                                  |                                        |

| Figure 7-5, Direction Control for Octets 1-8                                                                                                                                                                                                                                   |                                        |

| Figure 7-6, Direction Control for Octets 9-16                                                                                                                                                                                                                                  |                                        |

|                                                                                                                                                                                                                                                                                |                                        |

|                                                                                                                                                                                                                                                                                |                                        |

| Figure A-1, P1 Pin Configuration                                                                                                                                                                                                                                               | A-1                                    |

| Figure A-1, P1 Pin Configuration                                                                                                                                                                                                                                               |                                        |

|                                                                                                                                                                                                                                                                                |                                        |

|                                                                                                                                                                                                                                                                                | A-2                                    |

| Figure A-2, P2 Pin Configuration                                                                                                                                                                                                                                               | A-2<br>B-1                             |

| Figure A-2, P2 Pin Configuration                                                                                                                                                                                                                                               | A-2<br>B-1                             |

| Figure A-2, P2 Pin Configuration                                                                                                                                                                                                                                               | A-2<br>B-1<br>B-2                      |

| Figure A-2, P2 Pin Configuration<br>Figure B-1, M213 Front Panel I/O Signals<br>Figure B-2, M213 M/MA Interface Connector Configuration                                                                                                                                        | A-2<br>B-1<br>B-2<br>C-1               |

| Figure A-2, P2 Pin Configuration<br>Figure B-1, M213 Front Panel I/O Signals<br>Figure B-2, M213 M/MA Interface Connector Configuration<br>Figure C-1, M212 Front Panel I/O Signals                                                                                            | A-2<br>B-1<br>B-2<br>C-1               |

| Figure A-2, P2 Pin Configuration<br>Figure B-1, M213 Front Panel I/O Signals<br>Figure B-2, M213 M/MA Interface Connector Configuration<br>Figure C-1, M212 Front Panel I/O Signals                                                                                            | A-2<br>B-1<br>B-2<br>C-1<br>C-2        |

| Figure A-2, P2 Pin Configuration<br>Figure B-1, M213 Front Panel I/O Signals<br>Figure B-2, M213 M/MA Interface Connector Configuration<br>Figure C-1, M212 Front Panel I/O Signals<br>Figure C-2, M212 M/MA Interface Connector Configuration<br>Figure D-1, M1708 Connectors | A-2<br>B-1<br>B-2<br>C-1<br>C-2<br>D-2 |

| Figure A-2, P2 Pin Configuration<br>Figure B-1, M213 Front Panel I/O Signals<br>Figure B-2, M213 M/MA Interface Connector Configuration<br>Figure C-1, M212 Front Panel I/O Signals<br>Figure C-2, M212 M/MA Interface Connector Configuration                                 | A-2<br>B-1<br>B-2<br>C-1<br>C-2<br>D-2 |

### List of Tables

| Table 2-1, VXI Register Address Map 2-11                              |

|-----------------------------------------------------------------------|

| Table 2-2, M/MA Module EEPROM IDENT Words 2-22                        |

| Table 3-1, I/O Address Map/Command Summary3-8                         |

| Table 3-2, M-Module EEPROM IDENT Words                                |

| Table 4-1, I/O Address Map/Command Summary 4-11                       |

| Table 4-2, M/MA Module EEPROM IDENT Words 4-13                        |

| Table 4-3, 1PPS States Returned with the j Command       4-20         |

| Table 4-4, Floating Point Number Representation for DSIP         4-22 |

| Table 4-5, X72 Run Mode Commands 4-23                                 |

| Table 4-6, X72 Output Control Status Register Structure       4-24    |

| Table 6-1, I/O Address Map/Command Summary 6-11                       |

| Table 6-2, M-Module PROM IDENT Words 6-14                             |

| Table 7-1, M1714 Front Panel Pin-outs7-6                              |

| Table 7-2, Mating Connectors                                          |

| Table 7-3, M1714 Register Address Offset Assignments                  |

| Table 7-4, BIST Command Register Bit Definitions       7-12           |

| Table 7-5, BIST Status Register Bit Definitions                       |

This page was left intentionally blank.

# Chapter 1 INTRODUCTION

|                                                                                              | 3352<br>Version | VX405C                 | M212                                                                    | M213                                                                             | M1708                                                                                                | M210                                                                                                | M1714                                                                                                                                  |                  |

|----------------------------------------------------------------------------------------------|-----------------|------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Product<br>Configuration<br>1.) 407919<br>2.) 407919-001<br>3.) 407919-002<br>4.) 407919-003 |                 |                        |                                                                         |                                                                                  | n (RTCASS ve                                                                                         | ersion)                                                                                             |                                                                                                                                        |                  |

|                                                                                              |                 | different<br>following | iated by the                                                            | amount of I<br>rent versions of                                                  | M-module po                                                                                          | he versions are<br>pulation. The<br>ong with a table                                                | е                                                                                                                                      |                  |

|                                                                                              |                 |                        | integrate<br>and trigg<br>an integr<br>M210 Tr<br>The GPS               | es a Rubidium<br>ger distribution<br>ration of sever<br>igger Distribu           | oscillator, a G<br>into a single<br>al standard pr<br>tion board an<br>on includes a                 | PS timing rec<br>slot package.<br>oducts as sho<br>d GPS antenr<br>Motorola Once                    | cks, the 3352<br>eiver, and clock<br>The module is<br>wn below. The<br>na are optional<br>ore Timing2000                               | k<br>s<br>e I.   |

| General<br>Description                                                                       |                 |                        | discipling<br>provides<br>GPS tim<br>includes<br>location.<br>over time | ed 10MHz Ru<br>s two 1V rms s<br>ing receiver is<br>automatic s<br>An external p | bidium freque<br>inewave and<br>capable of tra-<br>te survey for<br>power input ke<br>ne GPS setting | ency standard<br>eight TTL leve<br>acking up to 1<br>r accurate ar<br>eps the Rubic<br>gs in memory | provides a GPS<br>d. The module<br>el outputs. The<br>2 satellites and<br>ntenna positior<br>lium very stable<br>from becoming<br>ver. | e<br>d<br>n<br>e |

|                                                                                              |                 |                        |                                                                         |                                                                                  |                                                                                                      |                                                                                                     |                                                                                                                                        |                  |

| Version    | VX405C | M212 | M213 | M1708 | M210 | M1714 |

|------------|--------|------|------|-------|------|-------|

| 407919     | X      | X    | X    | X     |      |       |

| 407919-001 | Х      | Х    |      | Х     |      |       |

| 407919-002 | X _    | X    | X    | X     | x    |       |

| 407919-003 | X      | Х    |      | X     |      | X     |

|             | This manual covers all four versions of the 3352. For a version that does not have a particular M-module associated with it, skip the corresponding section in the manual.                                                                                                                                                                                                                                                                      |                                                                                                                                                                                               |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| MTBF        | The following is the MTBF calculations f<br>that make up the 3352 followed by the<br>version. The MTBF was obtained using t<br>with calculations configured for MIL-HDB<br>and Method 1 Case 3 for calculation met                                                                                                                                                                                                                              | e MTBF for each 3352<br>he Relex 7.1.2 software<br>K-217 FN2 as the model                                                                                                                     |  |  |  |  |

|             | 1.) VX405C Carrier<br>2.) M1708<br>3.) M210<br>4.) M212                                                                                                                                                                                                                                                                                                                                                                                         | 62,622 hrs<br>150,000 hrs<br>199,508 hrs                                                                                                                                                      |  |  |  |  |

|             | 4.) M213<br>a.) M213 board<br>b.) M12 GPS receiver<br>5.) M212                                                                                                                                                                                                                                                                                                                                                                                  | 264,879 hrs<br>1,600,1000 hrs                                                                                                                                                                 |  |  |  |  |

|             | a.) M212 board<br>b.) Rubidium Module<br>6.) M1714                                                                                                                                                                                                                                                                                                                                                                                              | 926,476 hrs<br>174,720 hrs<br>765,387 hrs                                                                                                                                                     |  |  |  |  |

|             | The following is the calculated values for each of the 3352 variants:                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                               |  |  |  |  |

|             | 1.) 3352 w/ GPS training (407919)29,551 hrs2.) 3352 w/o GPS training (407919-001)33,967 hrs3.) 3352 w/ GPS training and PG dist(407919-002)25,740 hrs                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                               |  |  |  |  |

| Programming | A VXI <i>plug&amp;play</i> driver is available th<br>functions to configure, operate and get s<br>driver includes an interactive soft front part<br>the user to interactively control the 3352 fr<br>VXI host. Also included are 32-bit Window<br>allow the user to call the VXI Plug and Pla<br>programming environment including: (<br>LabWindows/CVI, and LabView. The<br>source code as well as help files to as<br>programming the module. | status of the 3352. The<br>nel application that allows<br>rom any Windows based<br>ws DLL and LIB files that<br>by driver from almost any<br>C, C++, Visual Basic,<br>driver is provided with |  |  |  |  |

|             | Various minimum system requirements must be met for use of the VXI <i>plug&amp;play</i> driver. These minimum requirements are specified in the VXI Plug and Play specification document VPP-2. In general, the minimum hardware requirements for the Windows framework are:                                                                                                                                                                    |                                                                                                                                                                                               |  |  |  |  |

|             | Must be 100% IBM PC compatible                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                               |  |  |  |  |

|             | <ul> <li>Must have an 80/86/33 MHz or d</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                              | reater CPU with floating                                                                                                                                                                      |  |  |  |  |

Must have an 80486/33 MHz or greater CPU with floating point

- Must have at least a 120-MB hard disk

- Must have a VGA or higher compatible monitor

- Must have at least 8-MB RAM (Racal Instruments recommends 16-MB)

- Must have a Windows compatible mouse

- Must have the capability to control a VXI system

In addition, the following are minimum software requirements must also be met:

- Microsoft Windows 95, 98, ME, NT, 2000, XP or higher

- VISA I/O Library Version 2.0 of higher (most recent version is recommended)

- Minimum VXI Resource Manager software needed to configure a VXI system

To install the VXI*plug&play* driver, run *Setup.exe* from the installation disks or from the downloaded files. Follow the instructions on the installation wizard to complete the installation. The recommended installation directory is the system VXIppp directory. The driver files will be installed on your system as follows:

| File               | Directory            | Description                                             |

|--------------------|----------------------|---------------------------------------------------------|

| ri3352_32.dll      | VXIpnp\WinNT\bin     | 32-bit Windows DLL                                      |

| ri3352.lib         | VXIpnp\WinNT\lib\bc  | Borland compatible C library                            |

| ri3352.lib         | VXIpnp\WinNT\lib\msc | Microsoft compatible C library                          |

| ri3352.h           | VXIpnp\WinNT\include | ANSI C header file                                      |

| ri3352.exe         | VXIpnp\WinNT\ri3352  | Soft front panel Executable                             |

| ri3352.c           | VXlpnp\WinNT\ri3352  | Driver source code                                      |

| ri3352sfp.c        | VXIpnp\WinNT\ri3352  | Soft front panel source code                            |

| ri3352.fp          | VXIpnp\WinNT\ri3352  | LabWindows\CVI interactive function panels              |

| ri3352.doc         | VXIpnp\WinNT\ri3352  | Driver documentation                                    |

| ri3352.hlp         | VXIpnp\WinNT\ri3352  | Driver help file                                        |

| ri3352sfp_help.hlp | VXIpnp\WinNT\ri3352  | Soft front panel help file                              |

| ri3352uir.uir      | VXIpnp\WinNT\ri3352  | Soft front panel user interface file for LabWindows/CVI |

| ri3352uir.h        | VXIpnp\WinNT\ri3352  | Header file for the soft front panel user interface     |

For details on the specific driver functions or on operating the soft front panel application, refer to the installed help files. If low-level (i.e. register level) programming details are needed for any of the modules that make up the 3352 (M212, M213, M1708, M210, M1714), refer to documentation for the specific module, which is contained in separate chapters of this manual.

The 3352 requests four VXI logical addresses from the resource manager. Each logical address refers to one of the four modules that make up the integrated unit. When accessing the VXI Plug and Play driver, only the base address (position A of the VX405C) should be used.

NOTE: The M210 Trigger Distribution Module is configured with the input thresholds set to fixed factory default levels. No programming is required for this module and thus the software driver does not refer to it.

# Chapter 2 VX405

| General<br>Description         | The VX405C is a single slot, register-based, C-size, VXIbus compatible carrier module that provides electrical and mechanical support for up to six single M or MA modules (M/MAs). Of these six M modules connections, four are used for a fully populated 3352. This is because the M210, M1714 and the M212 are double wide M modules and only one of the two connections is enabled. The connections that are enabled are A, C, D and E for a fully populated 3352. Each installed M/MA module appears as an independent VXI instrument to the VXI resource manager. Full VXI and MA-Module triggering and addressing is supported. |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Purpose of<br>Equipment        | This module provides a carrier function for the plug-in modules that make up the 3352 Rubidium system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Specifications of<br>Equipment |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Key Features                   | <ul> <li>Supports up to six (6) ANSI/VITA 12-1996 compliant<br/>single wide M or MA-modules, or any valid combination<br/>of 2, 3, or 4 wide modules</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                | <ul> <li>Supports extended M-Module functions (MA) such as<br/>extended 24-bit addressing for up to 16 Mbytes of<br/>memory, 32-bit data bus, and trigger signals for<br/>synchronization of MA-Modules</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                | <ul> <li>VXI A16, A24 and A32 addressing supported</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                | <ul> <li>D8, D16, and D32 accesses supported</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                | <ul> <li>Individual Logical Addressing of M/MA-modules</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                | <ul> <li>Isolated, filtered, and fused +5V, +12V, and -12V<br/>supplies for each M-module</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                | <ul> <li>±24V Auxiliary Power Connector (Rev. C or higher assemblies only)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                | Separate Software Programmable Interrupt Levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                | <ul> <li>MA-Module TRIGA and TRIGB can be connected to any<br/>VXI TTL Trigger Line through software control</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

- M/MA Module data access time < 800ns

- Front panel EMI shielding

- Interactive Mezzanine Control software available

#### **Electrical** The VX405C only requires the +5V power from the VXI back plane; however, ±12V may be required by installed M-modules and ±24V may be required if the auxiliary power connection is used. The carrier's peak module current (I<sub>PM</sub>) for the +5V supply is 1.2 amps. A total of 7.2A of +5V is available for the VXI backplane.

For electrical information on individual M/MA's, please reference each M/MA's documentation. The power requirements for each M/MA installed must be added to the VX405C's requirements for the total module's requirements.

|                         | -0001     |              | -0002                |

|-------------------------|-----------|--------------|----------------------|

|                         | Power off |              | Standard replaceable |

|                         | resetting |              | fuses                |

|                         | fuses     |              |                      |

|                         | Hold      | Trip Current |                      |

|                         | Current   |              |                      |

| Total Max. Current +5V  | 5A        | 10A          | 10A                  |

| Total Max. Current +12V | 2.5A      | 5A           |                      |

| Total Max. Current +12V | 2.5A      | <u>5</u> A   |                      |

|                               | +5V  | +12V | -12V | +24V | -24V |

|-------------------------------|------|------|------|------|------|

| Total Available from VXI Slot | 7.2A | 1.0A | 1.0A | 1.0A | 1.0A |

| Used by VX405C internal logic | 1.2A | 0A   | 0A   | 0A   | 0A   |

| -0001 fused level             | 5.0A | 2.5A | 2.5A | 1A   | 1A   |

| -0002 fused level             | 5.0A | 2.5A | 2.5A | 1A   | 1A   |

|                                                | +5V   | +12V | -12V |

|------------------------------------------------|-------|------|------|

| Allowed by specification per M-Module position | 1A    | 0.2A | 0.2A |

| -0001 fused level per position                 | 1.25A | 0.3A | 0.3A |

| -0002 fused level per position                 | 2A    | 1A   | 1A   |

# Mechanical

The mechanical dimensions of the module are in conformance with the VXIbus specification Rev. 1.4 for single slot 'C' size modules. The nominal dimensions are 233.35 mm (9.187 in) high x 340 mm (13.386 in) deep.

# Environmental The environmental specifications of the module are: Operating Temperature: 0°C to +55°C Storage Temperature: -40°C to +75°C Humidity: <95% without condensation</td> Installed M/MAs may differ in environmental specification. Refer to each individual M/MA's documentation for information.

| Bus Compliance                                                                                          |                                                                                                                                                                                                                                                       | the VXIbus Specification Revision 1.4<br>odules and with VMEbus Specification<br>7, IEC 821.                                                                                           |  |

|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                         | Manufacturer ID:                                                                                                                                                                                                                                      | FC1 <sub>16</sub> or VXI-IDENT value                                                                                                                                                   |  |

|                                                                                                         | Model Code:                                                                                                                                                                                                                                           | FF2 <sub>16</sub> or VXI-IDENT value                                                                                                                                                   |  |

|                                                                                                         | VXI Access Type:                                                                                                                                                                                                                                      | Register Based                                                                                                                                                                         |  |

|                                                                                                         | VXI Addressing:                                                                                                                                                                                                                                       | A16/A24/A32                                                                                                                                                                            |  |

|                                                                                                         | VXI Data Transfer:                                                                                                                                                                                                                                    | D8/D16/D32                                                                                                                                                                             |  |

|                                                                                                         | VXI Sysfail:<br>VXI Interrupts:                                                                                                                                                                                                                       | supported<br>ROAK or RORA,                                                                                                                                                             |  |

|                                                                                                         | VXI Interrupts.                                                                                                                                                                                                                                       | programmable levels                                                                                                                                                                    |  |

|                                                                                                         | VXI Local Bus:                                                                                                                                                                                                                                        | not used                                                                                                                                                                               |  |

|                                                                                                         | TTL Triggers:                                                                                                                                                                                                                                         | SYNC trigger protocol supported                                                                                                                                                        |  |

|                                                                                                         | Memory Requirements:                                                                                                                                                                                                                                  | M/MA dependent, up to 16Mbytes<br>(VXI 32Mbytes)                                                                                                                                       |  |

|                                                                                                         | M/MA-Module Compliance                                                                                                                                                                                                                                | D08, D16, D32, INTA, INTB,                                                                                                                                                             |  |

|                                                                                                         |                                                                                                                                                                                                                                                       | INTC, TRIGI, TRIGO, IDENT                                                                                                                                                              |  |

| Applicable                                                                                              | ANSI/VITA 12-1996Amerio                                                                                                                                                                                                                               | can                                                                                                                                                                                    |  |

| Applicable<br>Documents                                                                                 | National Standard for The Mezzanine Concept<br>M-Module Specification, Approved May 20, 1997<br>VMEbus International Trade Association<br>7825 E. Gelding Dr. Suite 104<br>Scottsdale, AZ 85260-3415<br>E-mail: info@vita.com URL: http:\www.vita.com |                                                                                                                                                                                        |  |

| Installation                                                                                            |                                                                                                                                                                                                                                                       |                                                                                                                                                                                        |  |

| Unpacking and<br>Inspection                                                                             | damage is apparent, ir                                                                                                                                                                                                                                | ule and inspect it for damage. If any<br>form the carrier immediately. Retain<br>king material for the carrier's inspection.                                                           |  |

| CAUTION<br>SENSITIVE ELECTRONIC DEVICES                                                                 | correct 3352 module op<br>EADS North America                                                                                                                                                                                                          | the package you received contain the<br>tion and the 3352 Users Manual. Notify<br>Defense Test and Services, Inc. if the<br>ed in any way. Do not attempt to install<br>a VXI chassis. |  |

| DO NOT SHIP OR STORE VEAR<br>STROWE DECENSISTATIC<br>ELECTROMAGNETIC, MAGNETIC OR<br>RADIOACTIVE FIELDS | electrostatic damage to                                                                                                                                                                                                                               | hipped in an anti-static bag to prevent<br>the module. Do not remove the module<br>unless it is in a static-controlled area.                                                           |  |

Handling Precautions The VX405C (3352) contains components that are sensitive to electrostatic discharge. When handling the module for any reason, do so at a static-controlled workstation, whenever possible. At a minimum, avoid work areas that are potential static sources, such as carpeted areas. Avoid unnecessary contact with the components on the module.

Installation of M\MA Modules M/MA modules must be installed before the VX405C (3352) is installed into the VXI system. To install modules, remove the VX405C's top shield and front panel covers as needed. *There is never a need to remove the VX405C's bottom shield*. Install M/MAs by firmly pressing the connector on the M/MA together with the connector on the carrier. Secure the M/MA through the holes in the bottom shield using screws provided with the M/MA. For installing M/MA modules in locations E or F, longer screws are provided (if necessary) to accommodate the standoffs required on the VX405C in those locations.

# WARNING: The VX405C supports MA-Modules that use three row interface connectors. M-Modules use only two rows connectors and must be correctly positioned to use rows A and B on the carrier. When using M-Modules, row C on the VX405C is left unconnected.

# Installation of VX405C Carrier (3352) Preparation for Reshipment Set the module's logical address and addressing mode as described in Chapter 2 sections Logical Address Selection and Address Space Selection. Insert the module into the appropriate slot according to the desired priority. Apply power. If no obvious problems exist, proceed to communicate with the module as outlined in Chapter 2 section Operating Instructions. Use the original packing material when returning the switching module to EADS North America Defense Test and Services, Inc. for servicing. The original shipping carton and the instrument's plastic foam will provide the necessary support for

safe reshipment.

2. If the original packing material is unavailable, wrap the switching module in an ESD Shielding bag and use plastic spray foam to surround and protect the instrument. Reship in either the original or a new shipping carton.

# Functional Description

General

The VX405C carrier provides a mechanical and electrical interface between a VXIbus system and up to six ANSI/VITA 12-1996 standard M/MA modules. The carrier provides VXI register configuration and access to the M/MA module's I/O Space and Memory (if present). Each M/MA is controlled separately and appears as a different logical address in the VXI environment. A simplified block diagram of the module is shown in **Figure 2-2**. The VX405C has no logical address or programmable registers associated with it, thus allowing the carrier to be completely transparent in the VXI system.

Figure 2-2, VX405C Functional Block Diagram

Interfaces The six M/MA locations interface electrically and mechanically with industry standard M/MA modules meeting the ANSI/VITA 12-1996 M-Module Specification (approved May 20, 1997). Each M/MA has its own I/O connector and is accessible through the front panel of the VX405C via the connector or a user provided cable.

# I/O and Memory Addressing

The VX405C supports D8 (Even/Odd), D16, and D32 data access as well as A16, A24, and A32 addressing. The VXI registers of the M/MAs are accessible in the A16 address space. The VXI Offset Register is used to map the M/MA I/O Space and MA Memory (if applicable) into the A24 or A32 addressing space. For MA's that support memory, the memory begins at the mid-point of the total memory required as shown in **Figure 2-3**.

#### Figure 2-3, Memory Organization

| Triggers                  | Each M/MA is allowed two trigger lines, TRIGA and TRIGB.<br>Triggers may be input or output. The VX405C Carrier provides<br>software programmable connection to any VXI TTL Trigger line<br>(SYNC Protocol). Each M/MA trigger can be enabled, logically<br>inverted, configured as input or output, and mapped to any of the<br>eight VXI TTL Trigger lines. |                                                              |                                                           |                                                            |                                               |                                                |                                            |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------|------------------------------------------------|--------------------------------------------|

| Interrupts                | Each M/MA can support of<br>ANSI/VITA 12-1996 Sp<br>programmed to an indi-<br>separately during interru-<br>priority for each interrupt<br>with M/MA slot A's interru-<br>slot F's Interrupt being the<br>to Chapter 2 section Inter                                                                                                                          | ecifica<br>vidual<br>pt ack<br>progra<br>upt beir<br>e lowes | tion.<br>interru<br>nowlec<br>mmed<br>ng the<br>st priori | Each<br>pt leve<br>lge cyo<br>to the<br>highest<br>ty. For | interr<br>el and<br>cles.<br>same<br>t priori | upt ca<br>is ha<br>A har<br>level, t<br>ty and | an be<br>andled<br>dware<br>begins<br>M/MA |

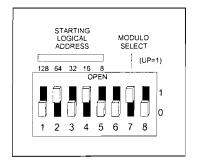

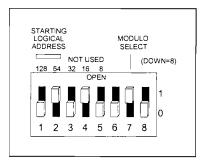

| Hardware<br>Configuration | The logical address, addre<br>M/MA-module locations n<br>carrier into the chassis.<br>switches described below                                                                                                                                                                                                                                                | nust be<br>The                                               | config<br>configu                                         | ured p<br>iration                                          | rior to<br>is dor                             | installi<br>1e usir                            | ng the                                     |

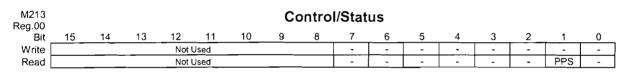

| Logical Address           | Each M/MA location has<br>position address switch.<br>the address for position A<br>or modulo-8 order, depen<br>Chapter 2 section Logical                                                                                                                                                                                                                     | The sel<br>. The o<br>ding or                                | ected lo<br>ther po<br>n the N                            | ogical a<br>ositions<br>lodulo \$                          | addres<br>follow<br>Select                    | s estat<br>in seq<br>switch                    | olishes<br>uential<br>n. See               |